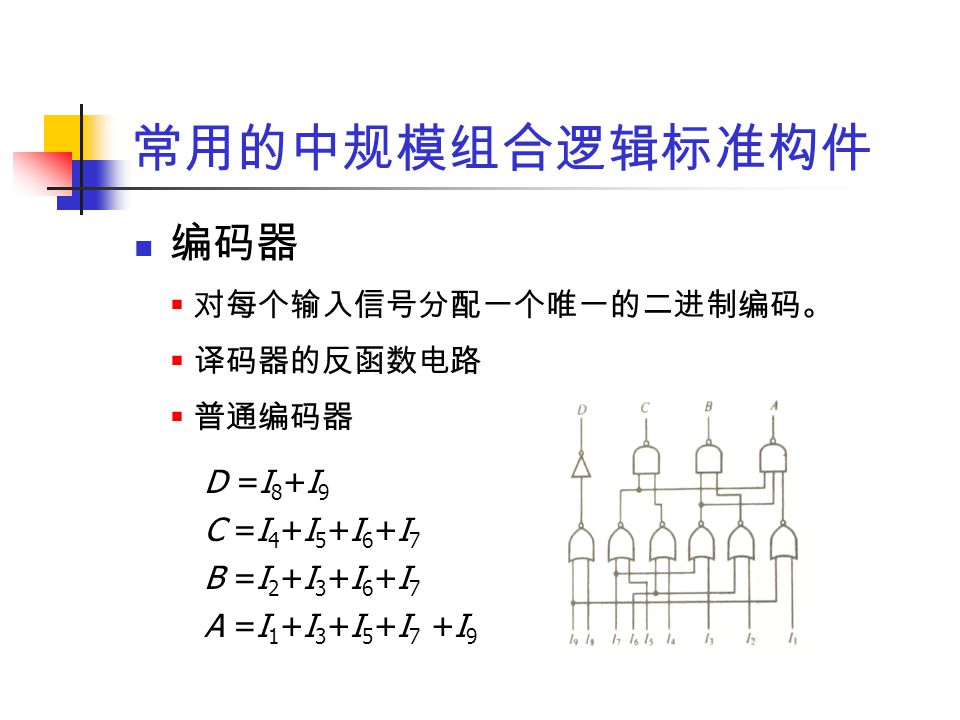

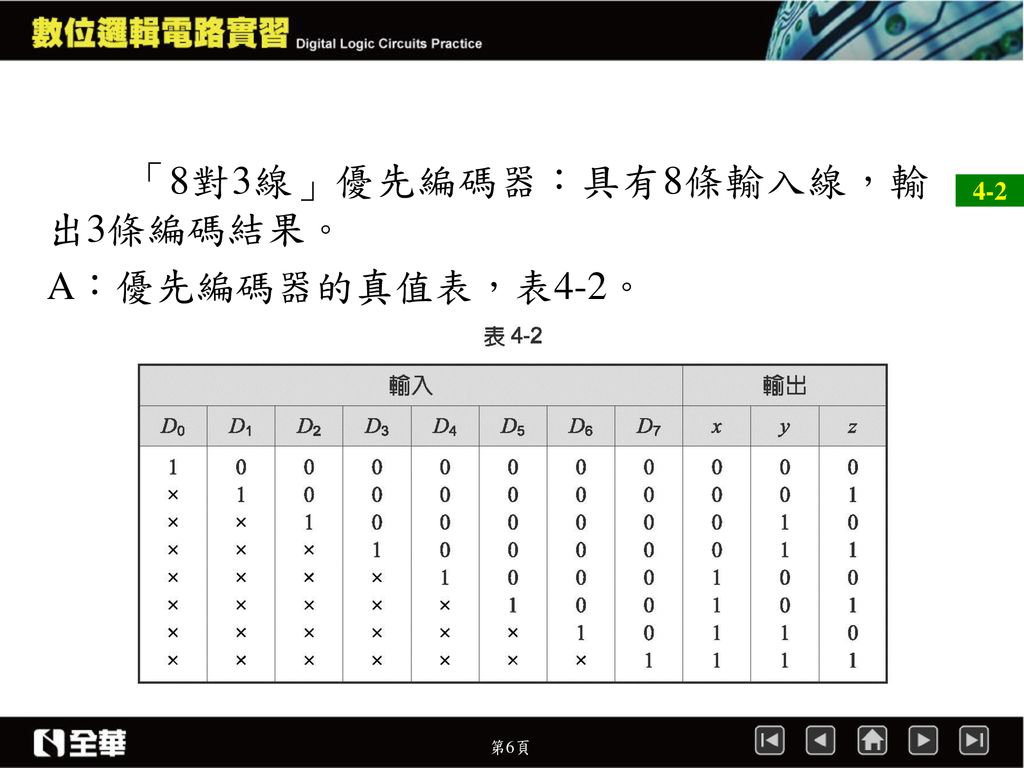

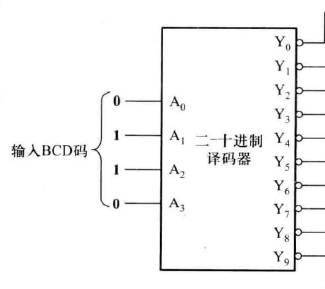

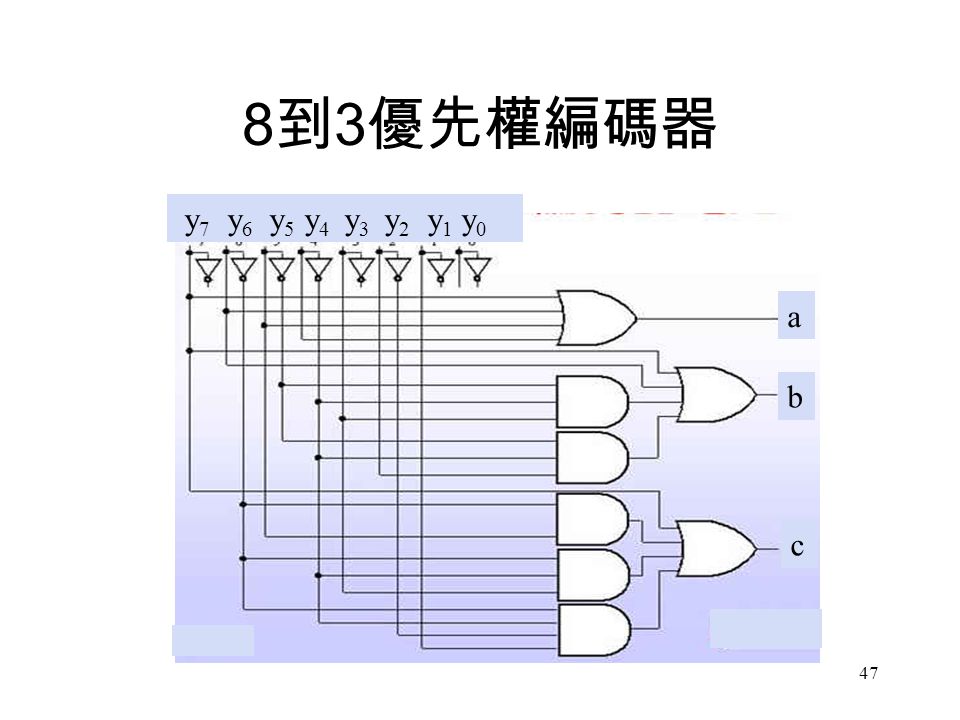

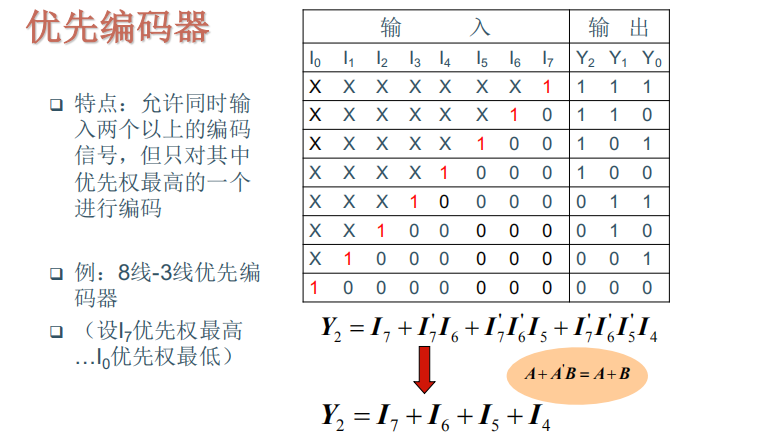

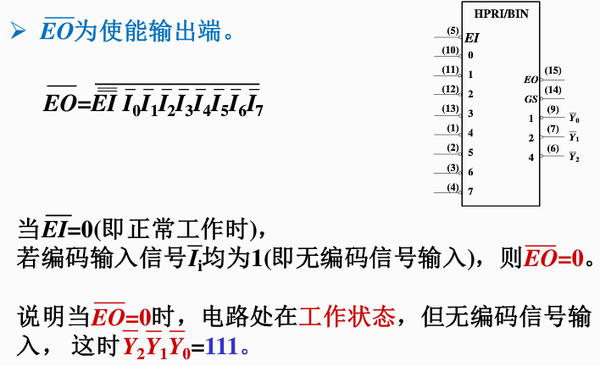

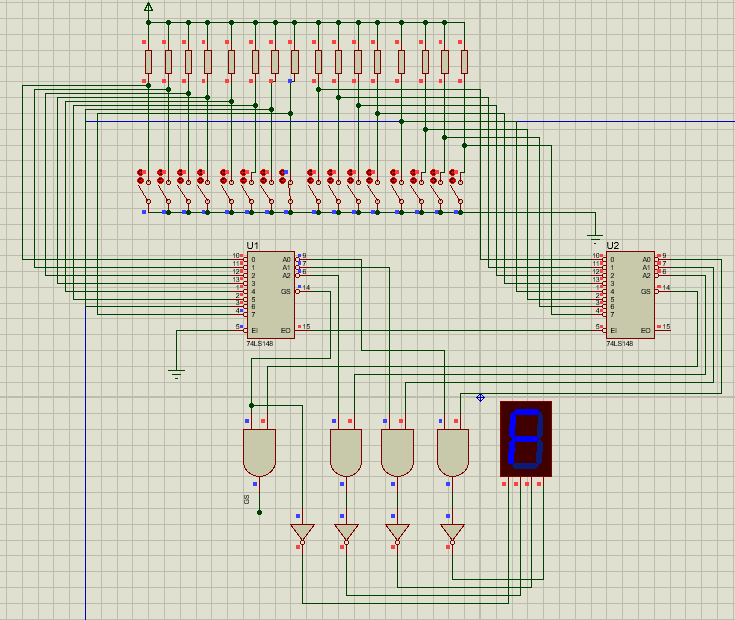

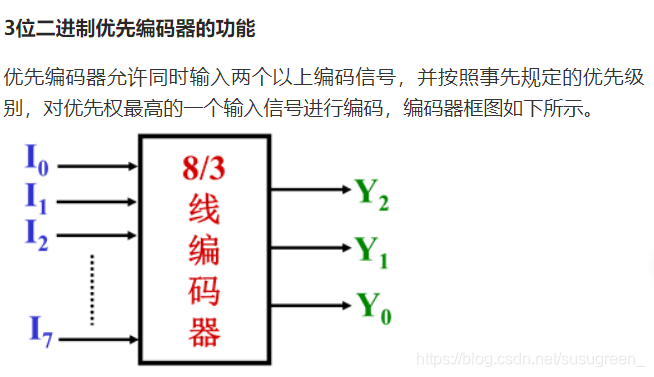

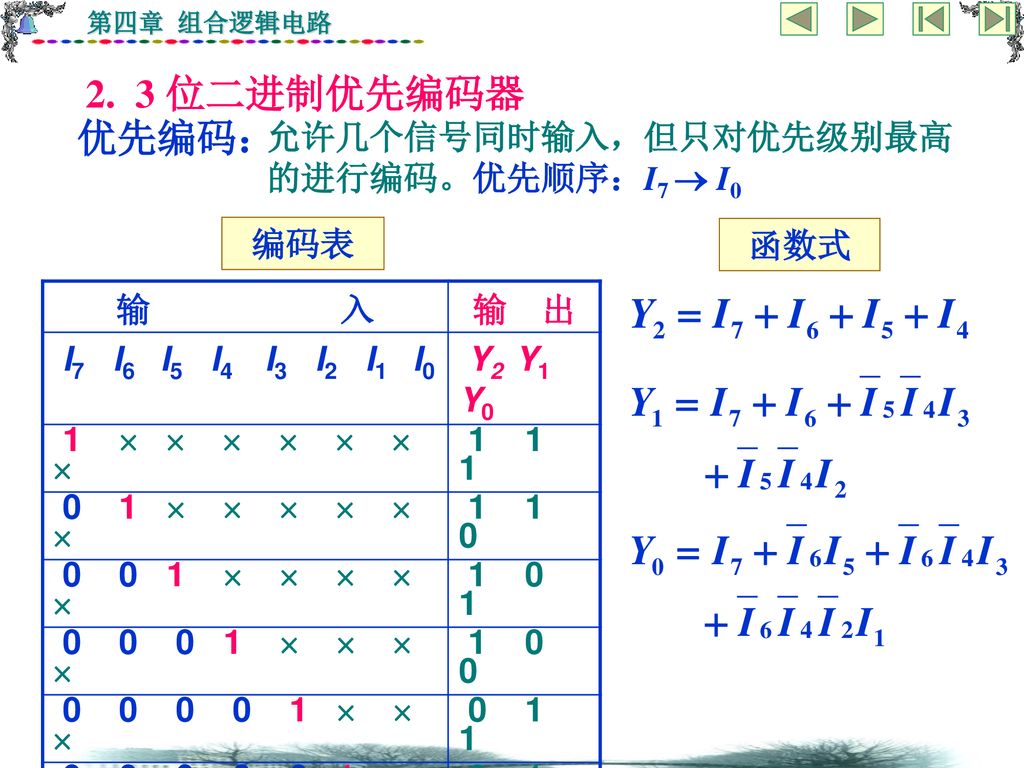

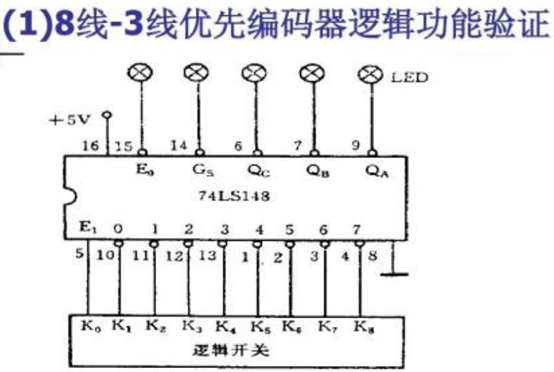

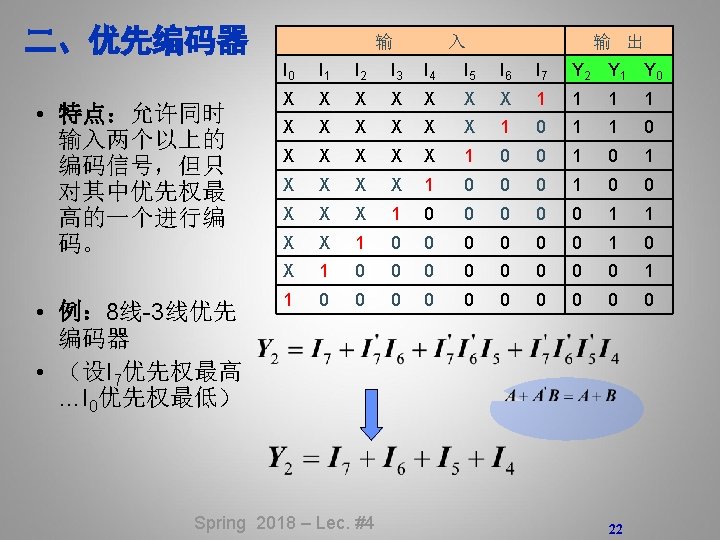

五、实验结果与分析 : 优先编码器(8 PriorityEncoder) 编译过程a)编译过程、调试结果 数字电路与逻辑设计实验报告 b)结果分析及结论这次尝试通过画图完成实验。新建一个 block,在others、primirily 找到 和input、output 器件完成对逻辑图的构画。URL在线编码解码工具(UrlEncode编码 和 UrlDecode解码) UrlEncode编码 UrlDecode解码 复制加密后的网址 广告 URL在线编码解码工具 1,本功能实现将Url进行:UrlEncode编码 和 UrlDecode解码 2,对Url进行编码后可以将一些特殊字符和汉字变为Encode编码格式 使用编码器74ls147,如何进行对十进制数0编码 : 图1245 二—十进制优先编码器74ls147的逻辑图 二—十进制优先编码器 二 十进制编码器74ls147的功能表中输出是按照反码

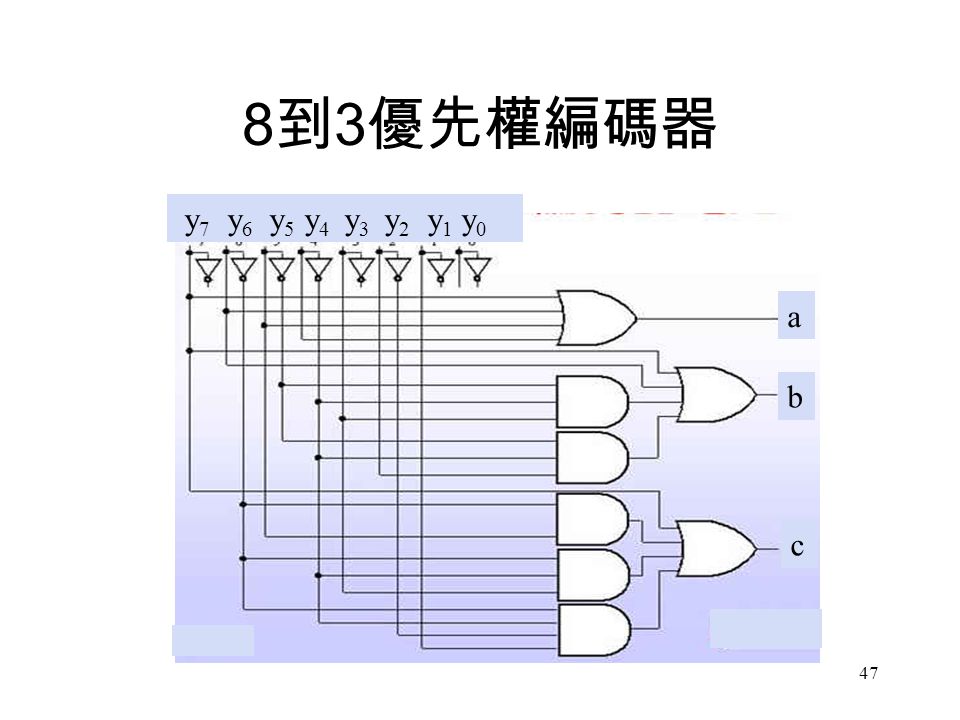

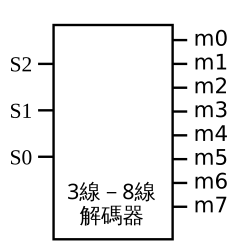

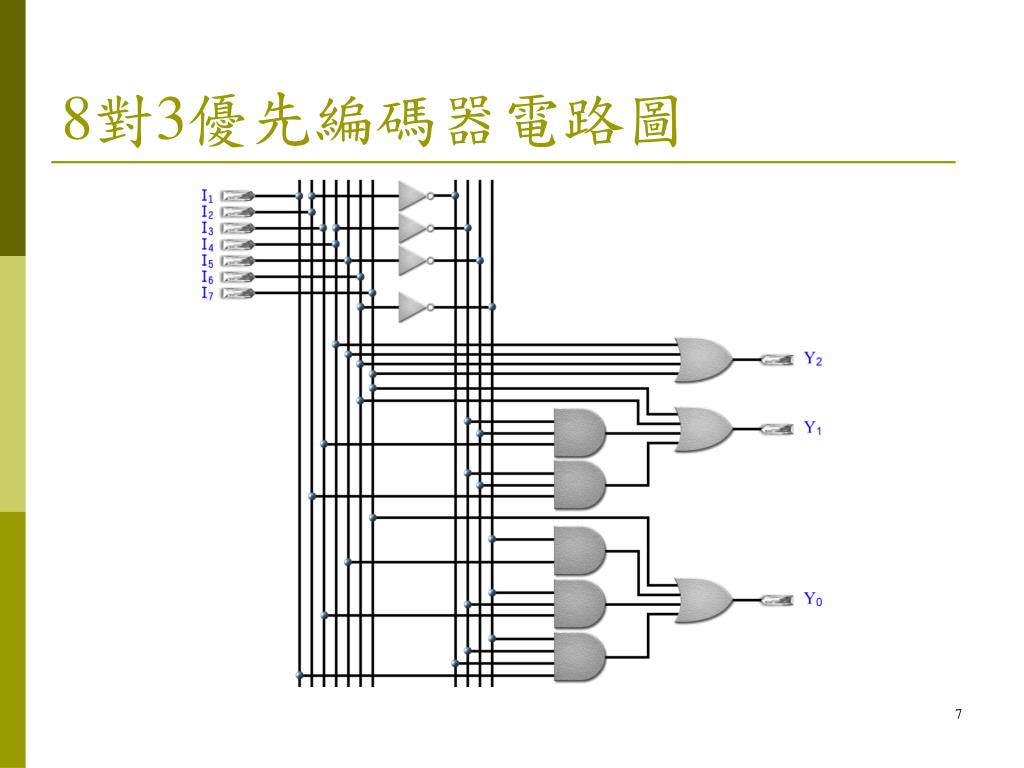

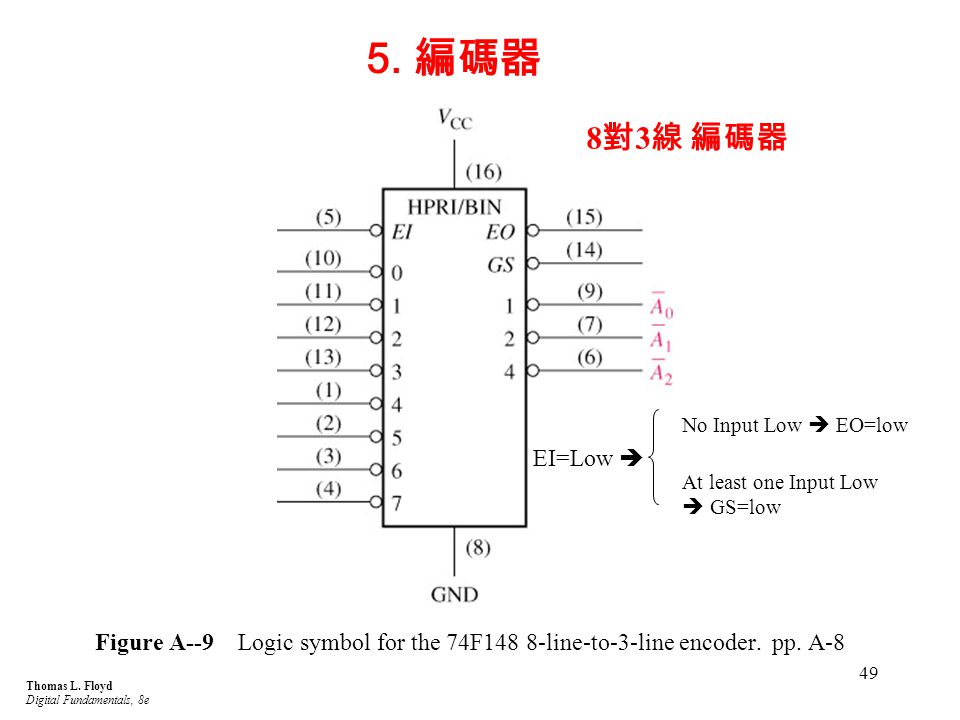

電子入門基礎知識之 8 3優先編碼器 每日頭條

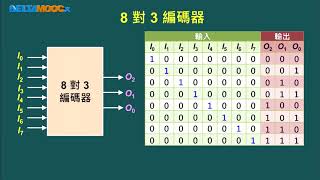

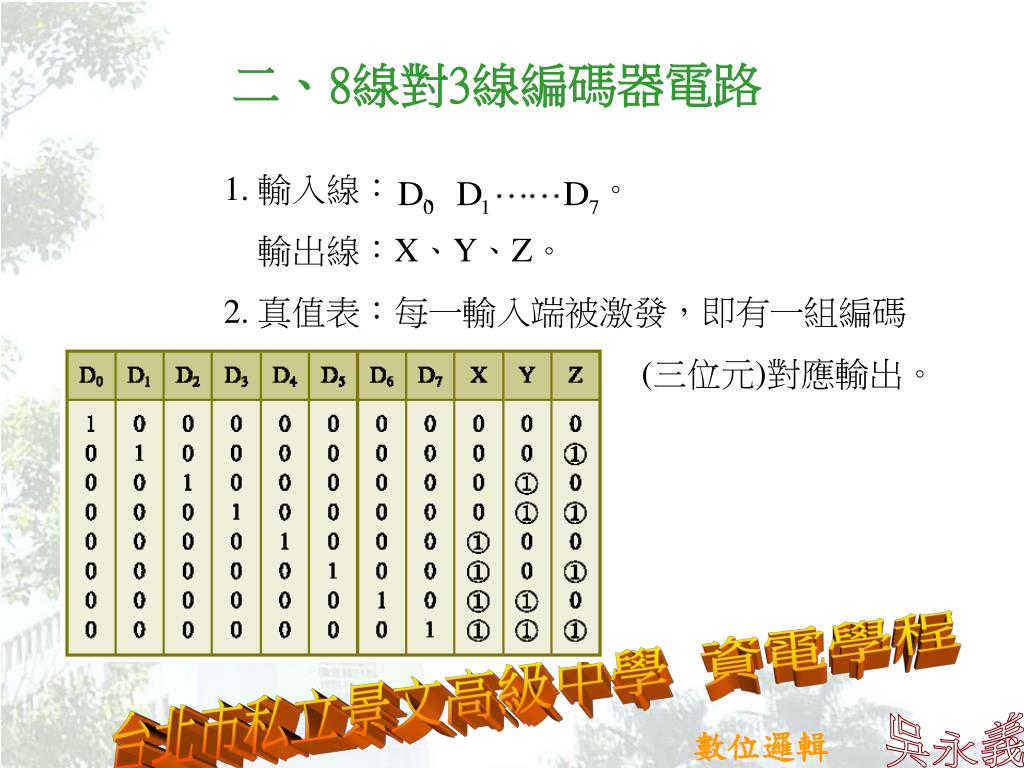

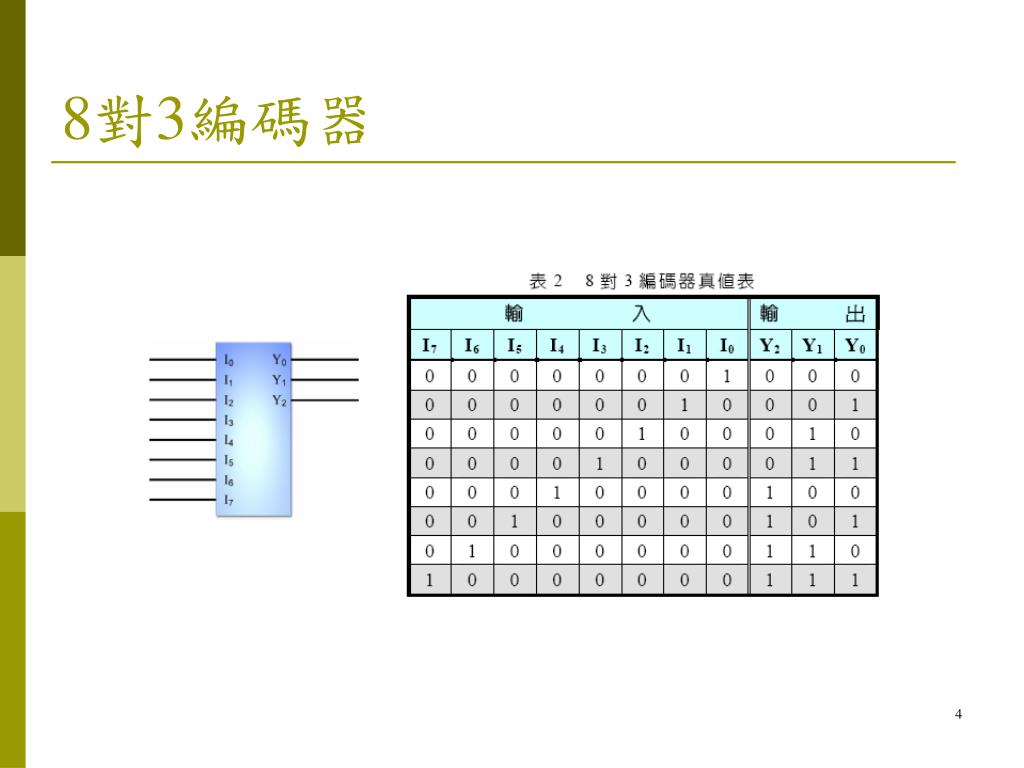

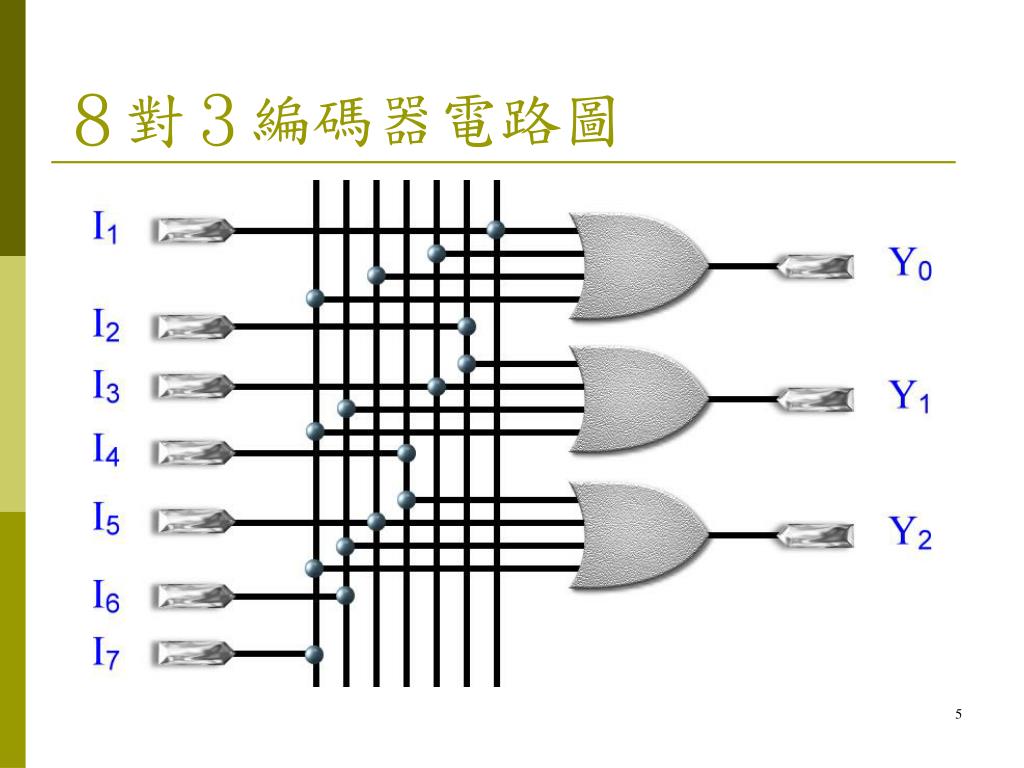

8对3编码器

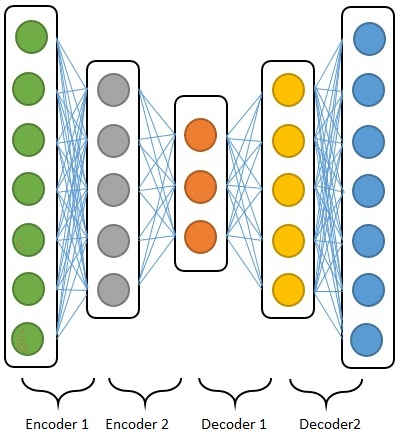

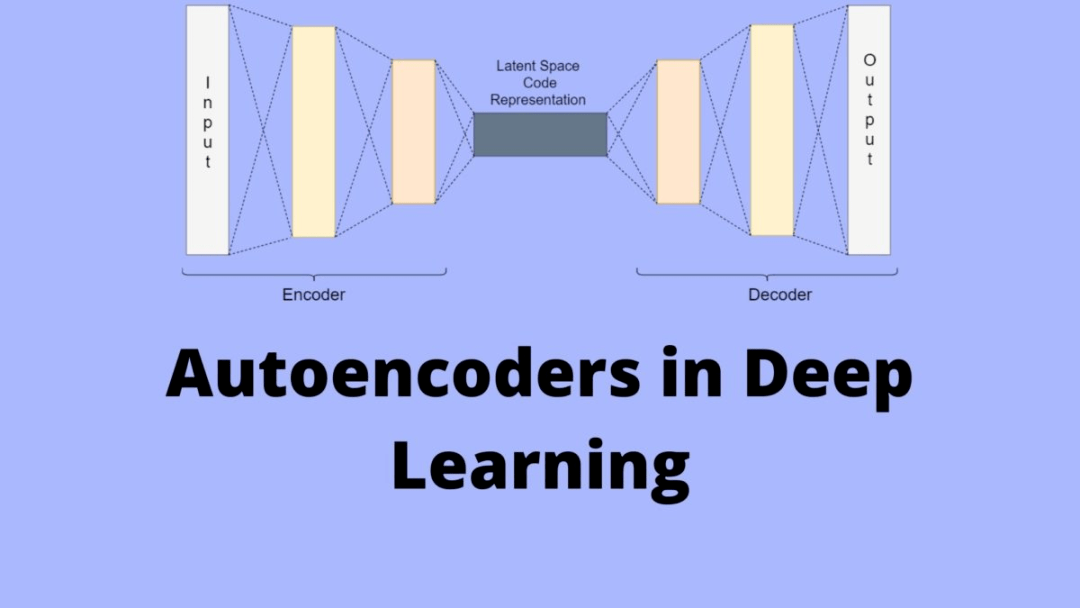

8对3编码器- 要避免此类干扰情况的出现,现场的编码器应由特定的工作电源独立供电,并且在输出功率选择上需做到足够大(编码器标示功耗的2倍以上);同时,选择的编码器应具有宽工作电压,例如 9~30Vdc 甚至 5~30Vdc 的工作电压,这表明编码器内部电路对工作电源的编码器用来分析输入序列,解码器用来生成输出序列。 图108描述了使用编码器—解码器将上述英语句子翻译成法语句子的一种方法。在训练数据集中,我们可以在每个句子后附上特殊符号""(end of sequence)以表示序列的终止。编码器每个时间步的输入依次

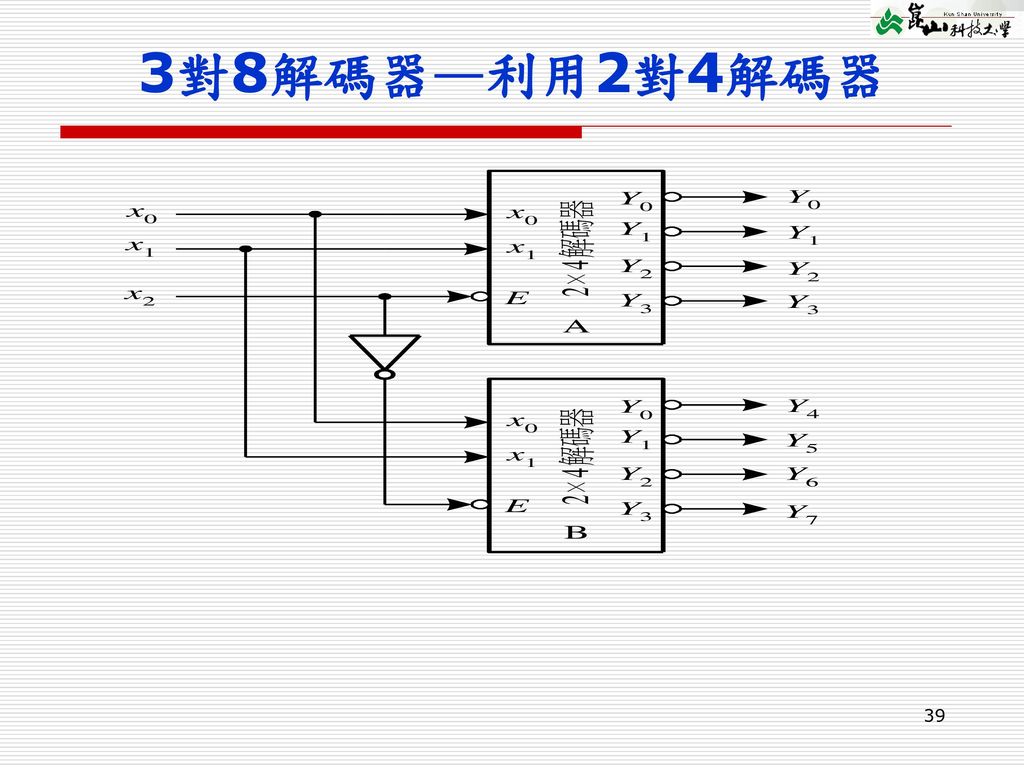

組合邏輯的函數functions Of Combination Logic Ppt Video Online Download

8线3线优先编码器74hc148 1 8线3线优先编码器74hc148 表41 74hchc138对发光二极管的控制 432 二~十进制译码器(又称bcd译码 器)二~十 3 三 译码器编码器编码器线 高柔屏蔽电缆2对3对4对5对4芯芯6芯8芯10芯伺服编码器线 编码器脉冲信号走的是高频,在选择电缆内芯时需要根据高频特性参数来选择电缆内芯的平方面积,而不是根据平方面积来选择电缆。 当机器脉冲信号传输在米以上时,必须选用编码器专用信号注解 这个模块的编码器和解码器默认保护输入和输出的顺序。仅当底层的容器未排序时才会失去顺序。 在 Python 37 之前, dict 并不保证有序,因此输入和输出通常都是乱序的,除非是明确地请求 collectionsOrderedDict 。 从 Python 37 开始,普通的 dict 会保留顺序,因此不必再为 JSON 的生成

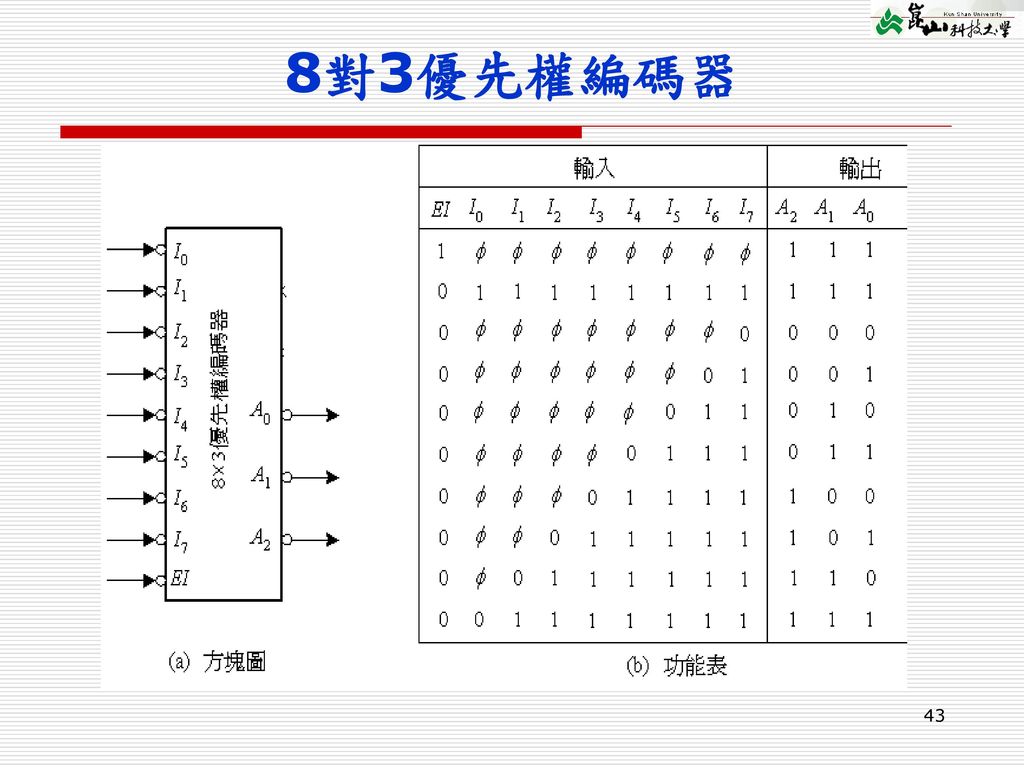

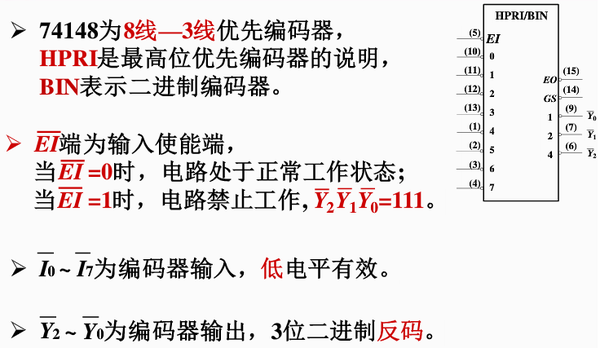

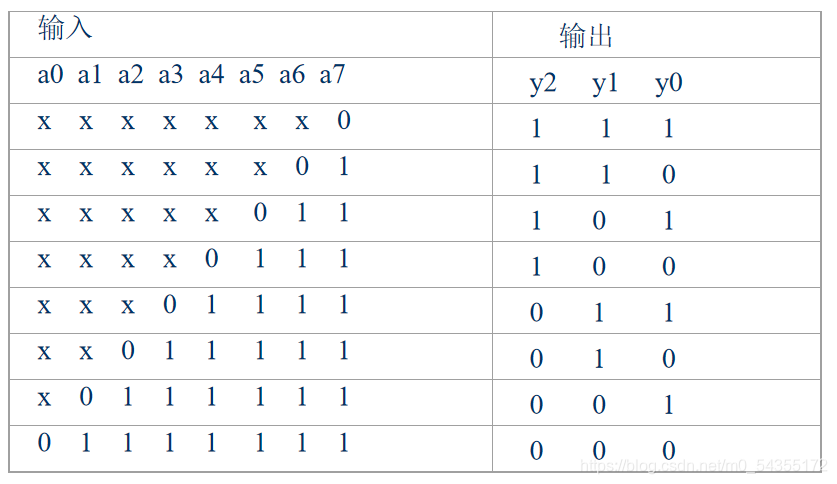

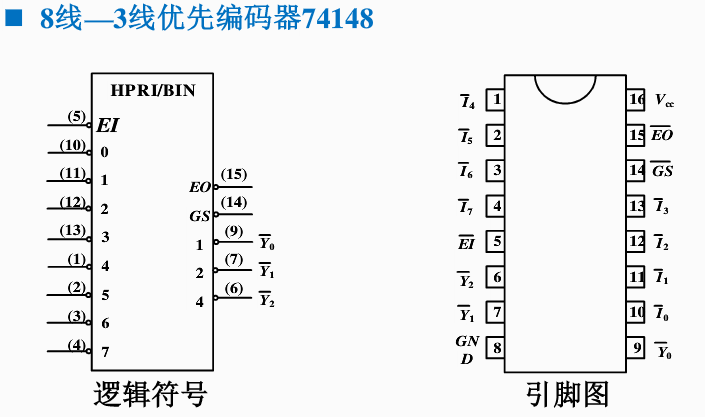

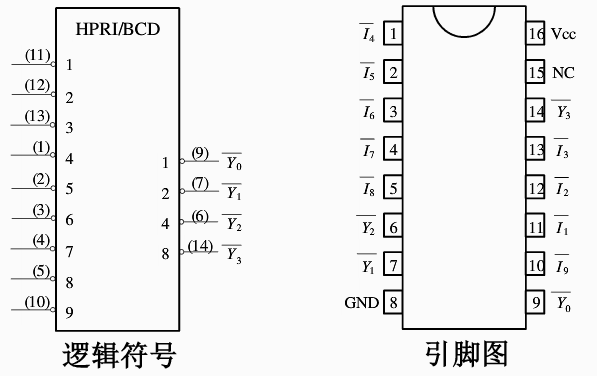

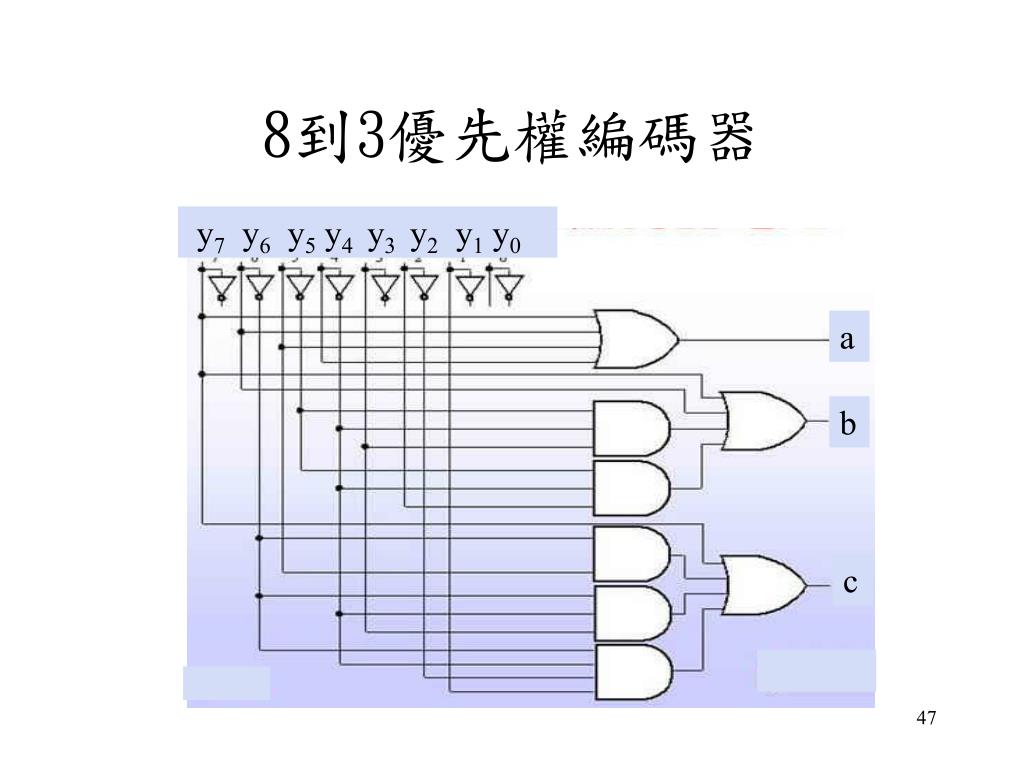

在数字逻辑中74ls148代表什么 : 感谢求助~ 74ls148是优先编码器 74ls148 为 8 线3 线优先编码器,共有 54/ 和 54/74ls148 两种线路结构型式, 将 8 条数据线(07)进行 3 线(421)二进制(八进制)优先编码,即对最高位数据线进行译码(3)编码器 如图43所示,74hc147h为10-4线优先(高位优先)编码器,当任意输入为低电平时,输出为相应的输入编号的8421码(bcd码)的反码。 图42 8路触发锁存电路。 图43 10-4线优先编码器 (4)译码驱动及显示单元 编码器实现了对开关信号的编码并以bcd码的形式 关注 展开全部 8线3线编码器,其实名字就给出了,是8个输入端,接8个按纽,有3位二进制代码输出,按纽0~7,对应的编码是000~111。 7 已赞过 已踩过 < 你对这个回答的评价是? 分享 新浪微博 QQ空间

此模块实现了 utf8 编解码器的一个变种:在编码时将把 utf8 已编码 bom 添加到 utf8 编码字节数据的开头。 对于有状态编码器此操作只执行一次(当首次写入字节流时)。 在解码时将跳过数据开头作为可选项的 utf8 已编码 bom。 8线3线编码器有几个输入,几位二进制代码输出 7 vhdl 8线3线优先编码器 1 EDA课程设计报告8线3线优先编码器 什么是编码器? 编码器是对旋转角度和线性位移进行编码的传感器。 检测旋转的编码器称为旋转编码器,检测线性位移的编码器称为线性编码器。 实际上,因为在大多数情况下使用旋转类型,所以当人们只说编码器时,它通常指的是旋转编码器。

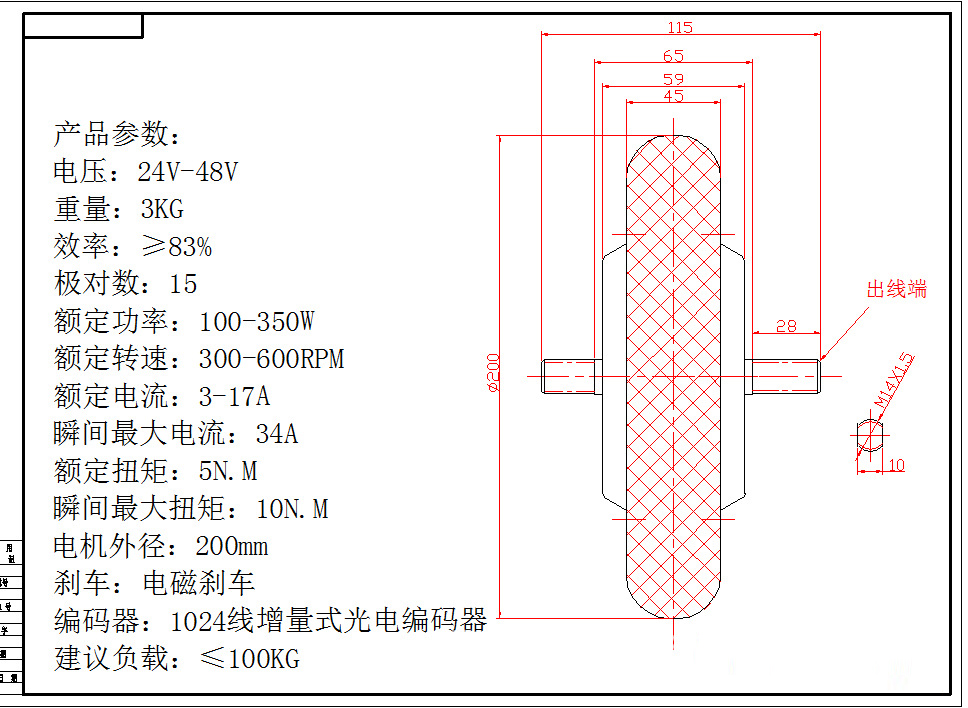

8寸内置编码器服务机器人agv小车伺服轮毂电机 常州问鼎电动车辆科技有限公司

多图解析 编码器计数原理与电机测速原理 面包板社区

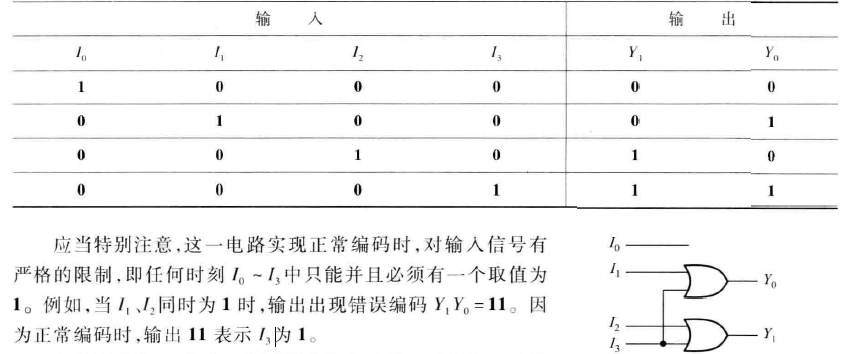

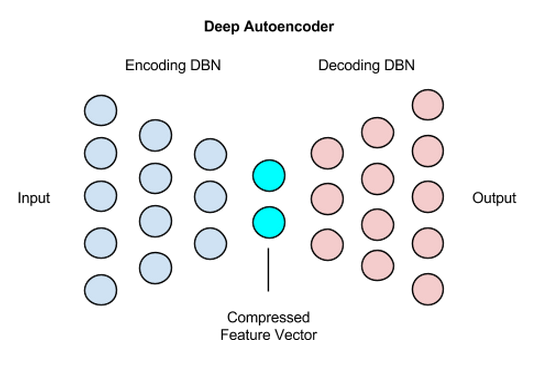

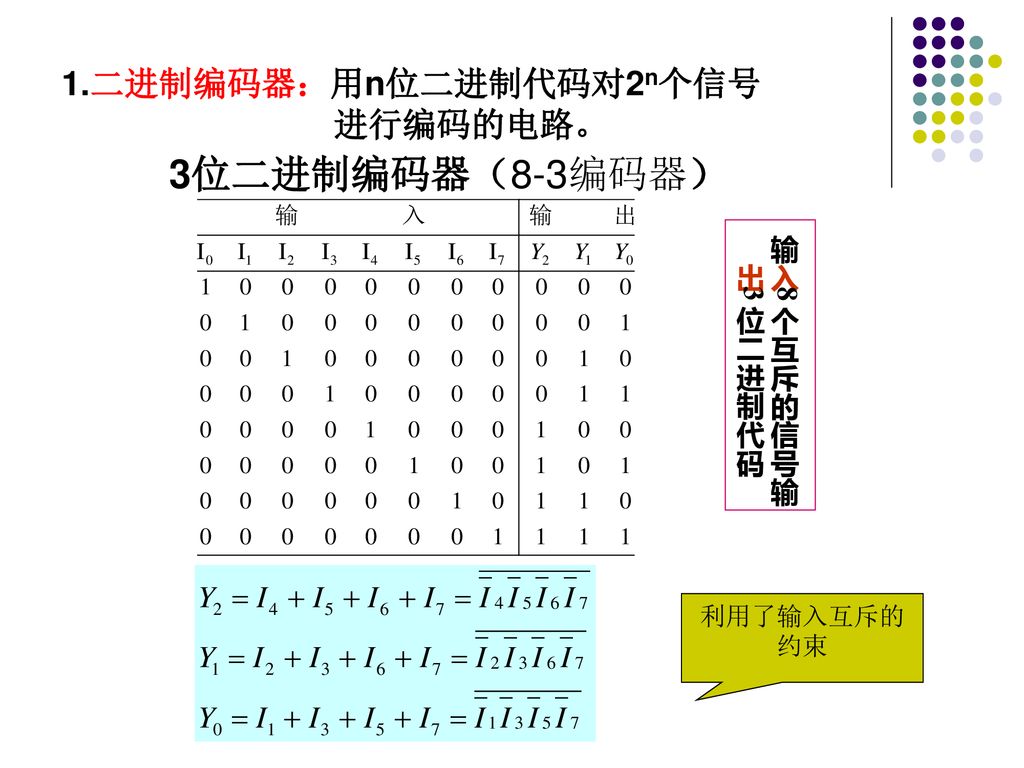

3、收缩自编码器 为了提高对训练集数据点周围小扰动的鲁棒性,收缩自编码器在基础自编码器上添加了正则项,另一个正则化自编码器的策略是使用一个类似系数编码器中的惩罚项 ,但 的形式不同: 这迫使模型学习一个在x变化小时目标没有太大变化的函数,因为这个惩罚只对训练数据适用,它所谓编码,就是在选定的一系列二值 代码中赋予每个代码以固定的含义,执行编码功能的电路统称为编码器。 实现 8 线 3 线编码器,它的功能是对输入端的 8 个信号进行编码,输出三位二进制数。 要求输入信号每次只有一个事 0, 其余 7 个是 1。_____ 74ls148是8线3三线优先级编码器,其引脚图以及工作原理如下 74LS48是输出高电平有效的7段显示译码器,其引脚图以及工作原理如下 关于优先编码器74LS148(即编码器的基本问题) _____ 1 这是说编码器的原理,因为编码器是将输入信号转化成二

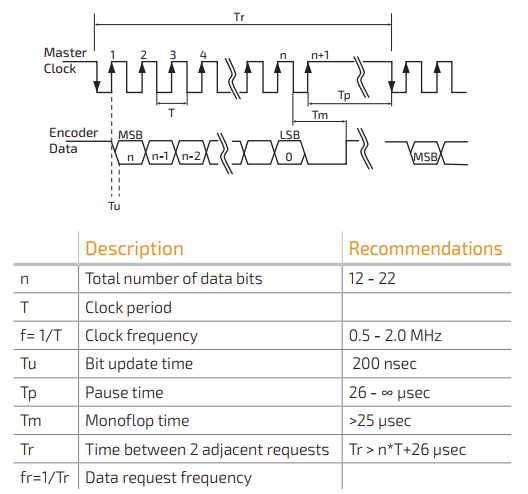

在伺服电机中常用的几种编码器协议 大大通

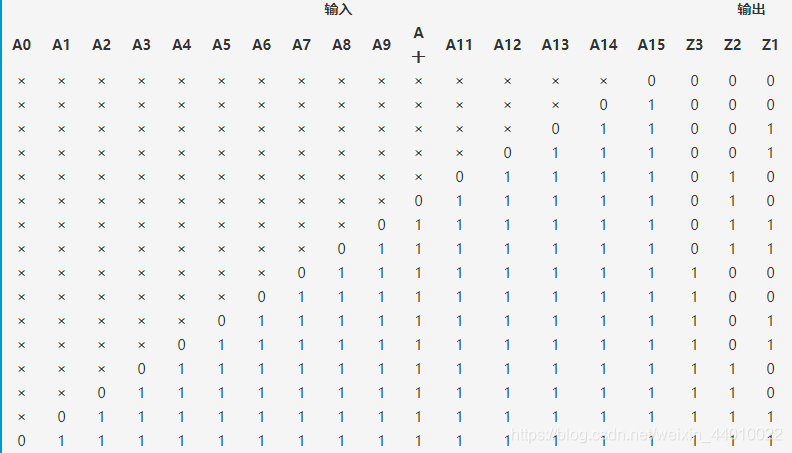

数字电路两片 16 4线编码器 病房管理 Weixin 的博客 Csdn博客

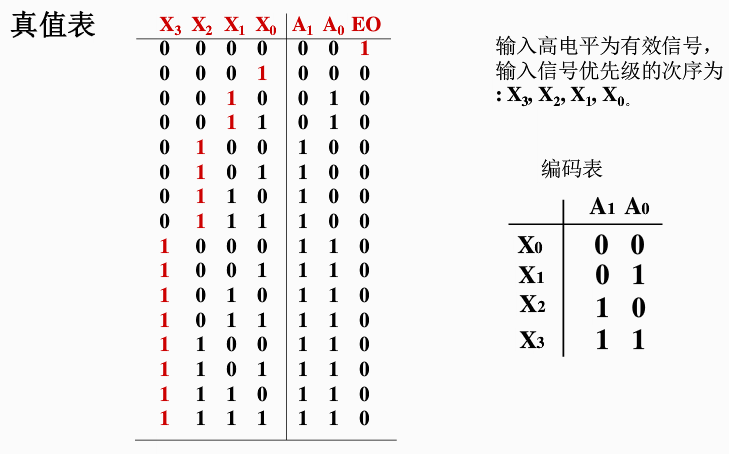

030 库伯勒kubler编码器 具体成交价以合同协议为准 东莞市优先级编码器有许多不同的形式,例如一个8输入优先级编码器及其真实值表,如下所示。 8至3位优先编码器 优先级编码器以标准ic形式提供,而ttl 74ls148是8位至3位优先级编码器,具有八个活动的low(逻辑" 0")输入,并在其输出处提供输入最高等级的3位代码。优先编码器74HC148的8个输入都是1的话,输出会是什么呢 : 1 这是说编码器的原理,因为编码器是将输入信号转化成二进制形式,即每一个输入都对应一个唯一的二进制输出,n位二进制能表示2的n次方个数,所以对多允许有2的n次方个输入值2优先级,就是说有高优先级

第二章组合逻辑梁华国计算机与信息学院计算机系统结构研究室workroom Socweb Index Php Ppt Download

第4章

优先编码器课程设计doc,东北石油大学课程设计任务书 课程 硬件课程设计 题目 优先级编码器设计 专业 计算机科学与技术 姓名 学号 主要内容、基本要求等 一、主要内容: 利用EL教学实验箱、微机和QuartusⅡ软件系统,使用VHDL语言输入设计。1 杨刚,龙海燕现代电子技术VHDL与数据 采用 VHDL 语言 编写 的,基于FPGA平台的简单的 优先编码器 完整程序,已编译通过,结果正确。 优先编码器 0319 基于 vhdl 的 优先编码器 ,适用于初学者与课堂作业,这是我在数电课上写的,通俗易懂 两台电机编码器出线的颜色是一样的 按照相同的接线 ecmac604rs可以用 ecmac604rs不可以用 且 伺服驱动器报警 al011 (位置检出器异常) 伺服驱动器是asdab2

74ls148 74ls148 是8 線 3 線優先編碼器 共有54 百科知識中文網

數位電路設計 蕭宇宏 U07 組合邏輯電路 11 編碼器電路 Youtube

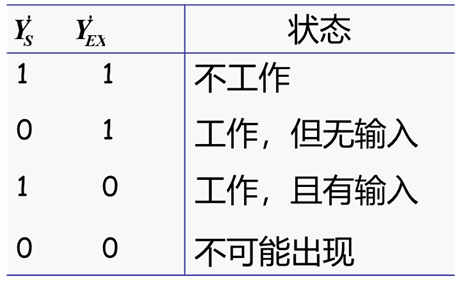

74LS148是带有扩展功能的线优先 编码器 ,它有8个信号输入端,3个二进制码输出端,一个输入使能端,一个选通输出端和一个扩展端。 使能端为"0"时,该芯片被选中,否则不被选中。Ttl 编码器输入 (x31) 电缆应该有至少4 对电缆。 第5 对电缆是 vcc 和 0v 。 * 两根线焊接到同一个管脚上。 ttl 编码器输入 (x31) 电缆对编号 信号名称 x31 插座管脚 (9针) 备注 1 a 1 a 6 2 b 2 b 7 3 z 3 z 8 4 vcc_enc_1 5 com_c 9 5 vcc_enc_1* 5* 可选 com_c 4 可选 可选 fen01 x31 a ab贵州大学实验报告 学院: 姓名 实验时间 实验项目 名称 专业: 学号 指导教师 班级: 编码器 实验组 成绩 实 1、学习编码器的功能与定义,学习 Verilog 或 VHDL 语言 验 2、熟悉利用 quartusII 开发数字电路的基本流程和 quarterII 软件的相关操作 目 3、学会使用 vector wave 波形仿真 的 实 验 软

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

8 3编码器 3 8译码器的verilog实现 Weixin 的博客 程序员宅基地 程序员宅基地

_____ ,,74ls148,是8线3线优先编码器,双列16脚封装 ic,外观有标准型和贴片封装类型74ls147是10线4线优先编码器,同样是双列16脚ic 74hc148和74ls148的性能及其区别 _____ 它是个 八线三线 优先级编码器74hc是兼容cmos电平的,供电3~12v ;74ls是兼容ttl电平的,供电45~55v 基本在数字逻辑中74ls148代表什么 : 感谢求助~ 74ls148是优先编码器 74ls148 为 8 线3 线优先编码器,共有 54/ 和 54/74ls148 两种线路结构型式, 将 8 条数据线(07)进行 3 线(421)二进制(八进制)优先编码,即对最高位数据线进行译码 图31 优先编码器功能仿真图 对其仿真图进行仿真分析:din 为输入信号组,它由din7din0 八个输入信 号组成。output 为输出信号组, 它由output2output0 三个二进制代码输出信 号组成。 enable 时编码器工作,当使能端为1时输出 高阻状态。

编码器 常用中规模集成电路 Msi 数电 知乎

電子入門基礎知識之 8 3優先編碼器 每日頭條

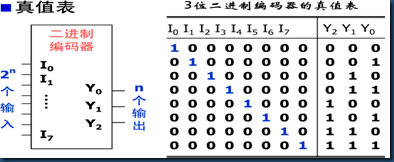

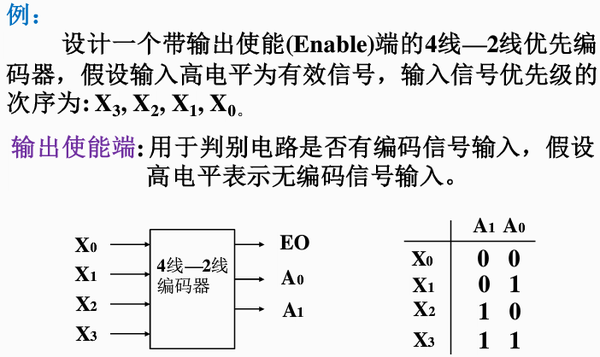

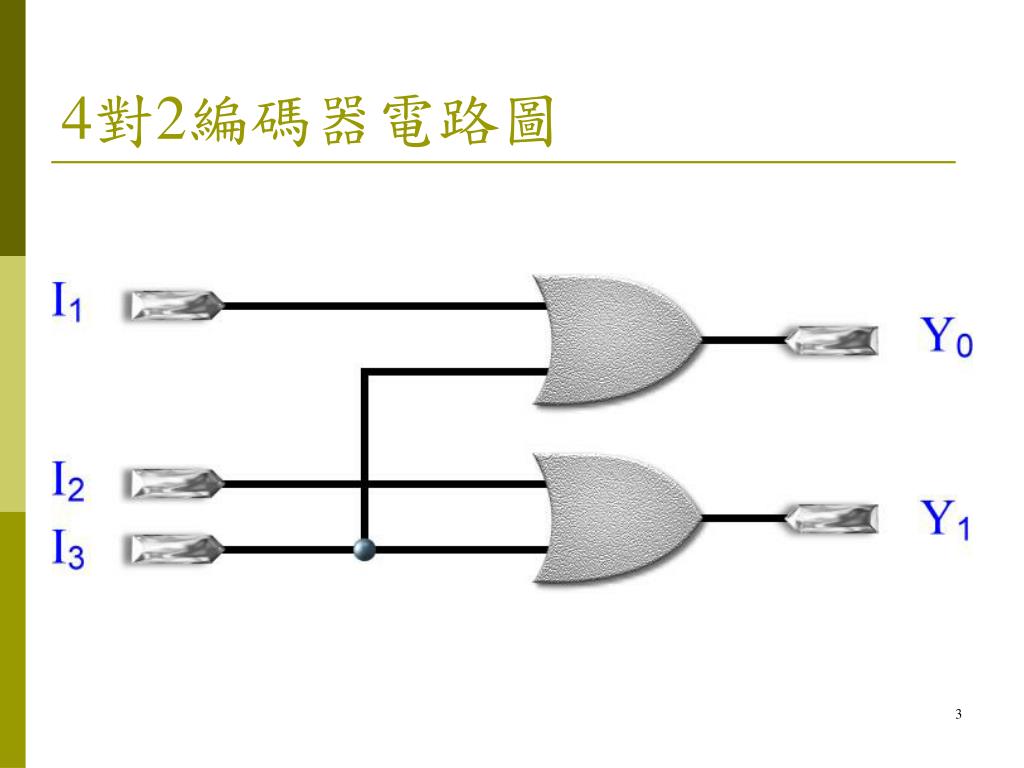

(5)具有手动和自动清零功能 使用编码器74LS147,如何进行对十进制数0编码 ?>> 1 半导体类型a本征半导体b掺杂半导体 性质热敏性,光敏性,掺杂性2 PN结具有单向导电性,加正电压(正向偏置),导通,电荷区变宽3 单晶硅中加砷或磷形成N型,空穴为多子,自由电子少子3 使用编码器74LS147,如何进行对十进制数0编码 : 1 半导体类型a本征半导体b掺杂半导体 性质热敏性,光敏性,掺杂性2 PN结具有单向导电性,加正电压(正向偏置),导通,电荷区变宽3 单晶硅中加砷或磷形成N型,空穴为多子,自由电子少子3 将PN结用玻璃或塑料外壳封装编码器 :实现编码的数字电路,把输入的每个高低电平信号编成一组对应的二进制代码。 设计一个输入为8个 高电平有效 信号,输出代码为原码输出的3位二进制编码器。 化简逻辑表达式: 由逻辑表达式可以得出,普通的编码器用或门即可实现。

74ls148逻辑图 万图壁纸网

数电第四章总结 组合逻辑电路 吟游诗人 吟唱生命的不朽 Csdn博客

基于v hdl 的 优先 编码器 ,适用于初学者与课堂作业,这是我在数电课上写的,通俗易懂 编码器 和 38 译码器的设计 01 有一个 编码器 和一个 38 译码器,使用V HDL 语言编写在MUX PLUS2上实现的 1?二进制编码器(p73) (2) 8—3线优先编码器 8/3优先编码器,典型芯片。(p74) 4 二–十进制优先编码器 (典型芯片为) 二?译码器 译码器的用途: 2? Verilog HDL 之 编码器原理: 在数字系统中,常常需要将某一信息(输入)变换为某一特定的代码(输出)。把二进制码按一定的规律排列,例如8421码、格雷码等,使每组代码具有一特定

二 相關知識在數位系統中 資料的表示方式通常是以0與1這兩種基本型態組合而成的 資料若要作處理 則必須將它轉為處理單元所能接受的型式 碼 此即所謂的 編碼 Encode 可以完成此編碼工作的電路稱為編碼器 Encoder 而當處理單元將資料處理完之後 則必須將它呈現

8 3编码器 3 8译码器的verilog实现 Sasha Xu 博客园

>> 74ls147是104位编码器,图片发不上了,需要的话q我~ 使用编码器74ls147,如何进行对十进制数0编码 ?>> 1 半导体类型a本征半导体b掺杂半导体 性质热敏性,光敏性,掺杂性2 pn结具有单向导电性,加正电压(正向偏置),导通,电荷区变宽3 单晶硅中加砷或磷形成n型

连载 Fpga Verilog Hdl 系列实例 8 3优先编码器 让linux飞一会儿 博客园

数字电路基础那些事1 组合逻辑 从译码器到编码器 三点羊羽 博客园

干货 浅析伺服编码器的分辨率和精度 面包板社区

Www Cyut Edu Tw Yfahuang Chap04 Pdf

電子入門基礎知識之 8 3優先編碼器 每日頭條

數位邏輯學 第八章

Vhdl 8 3优先编码器 M0 的博客 Csdn博客

数字电路基础那些事1 组合逻辑 从译码器到编码器 三点羊羽 博客园

增量编码器act50 A B 8 增量型编码器 华尔圣15年专注编码器制造

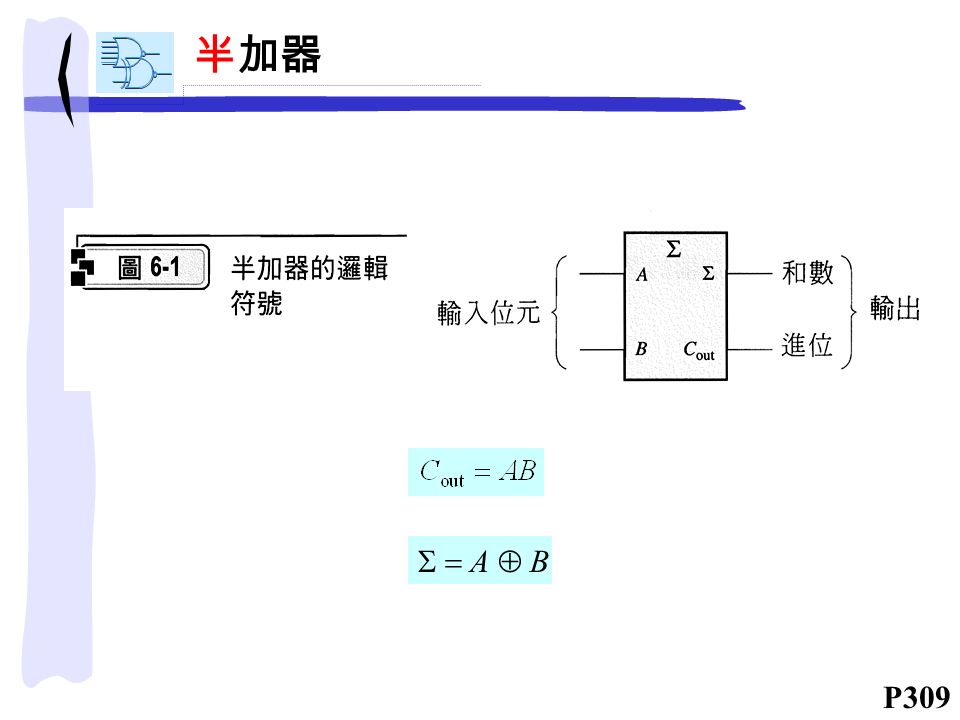

6 1 基本加法器6 2 平行二進位加法器6 3 比較器6 4 解碼器6 5 編碼器6 6 數碼轉換器6 7 多工器 資料選擇器 6 8 解多工器6 9 同位元產生器 檢查

6 4 1 74ls148编码器介绍

組合邏輯的函數functions Of Combination Logic Ppt Video Online Download

Http Www Ycvs Ntpc Edu Tw Ezfiles 0 1000 Img 112 Pdf

電子入門基礎知識之 8 3優先編碼器 每日頭條

移动机器人 2 Base Controller 旋转编码器 华为云

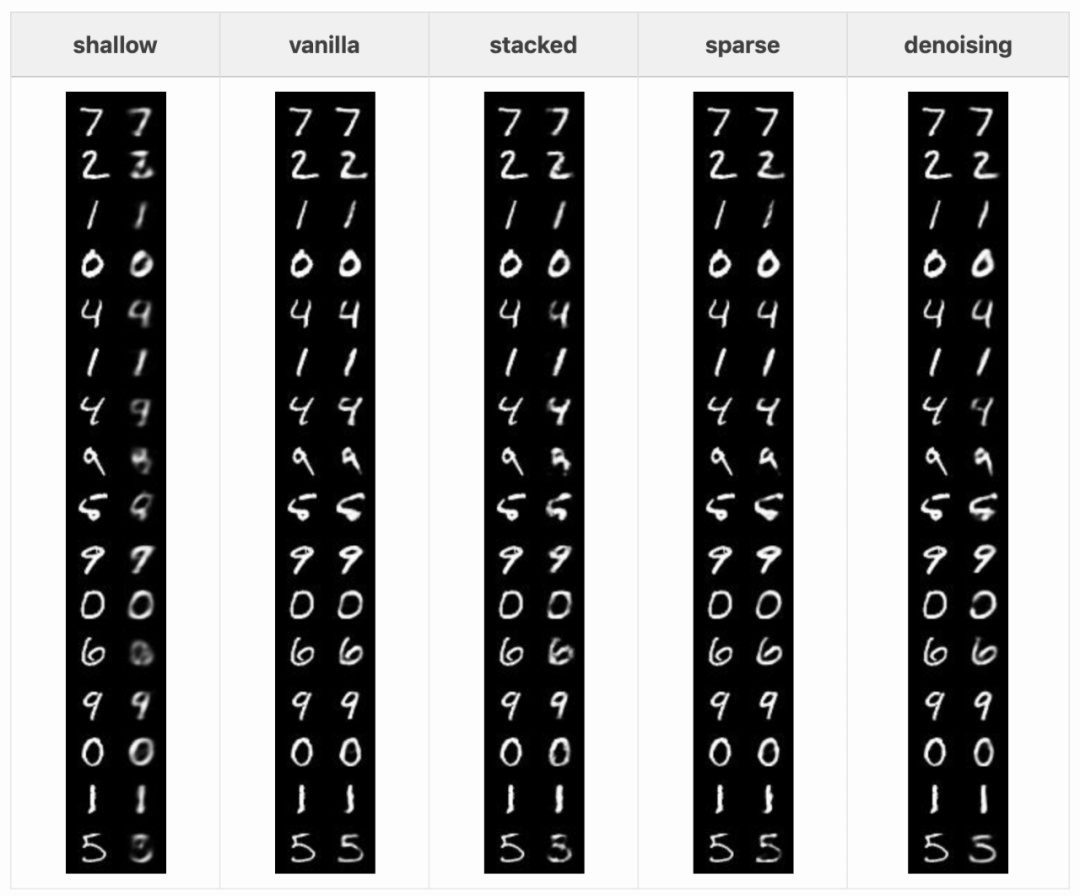

自动编码器一览 一 Kyon Huang 的博客

基于vhdl的旋转编码器接口电路的实现 可编程逻辑 与非网

数字电路笔记 摸黑干活

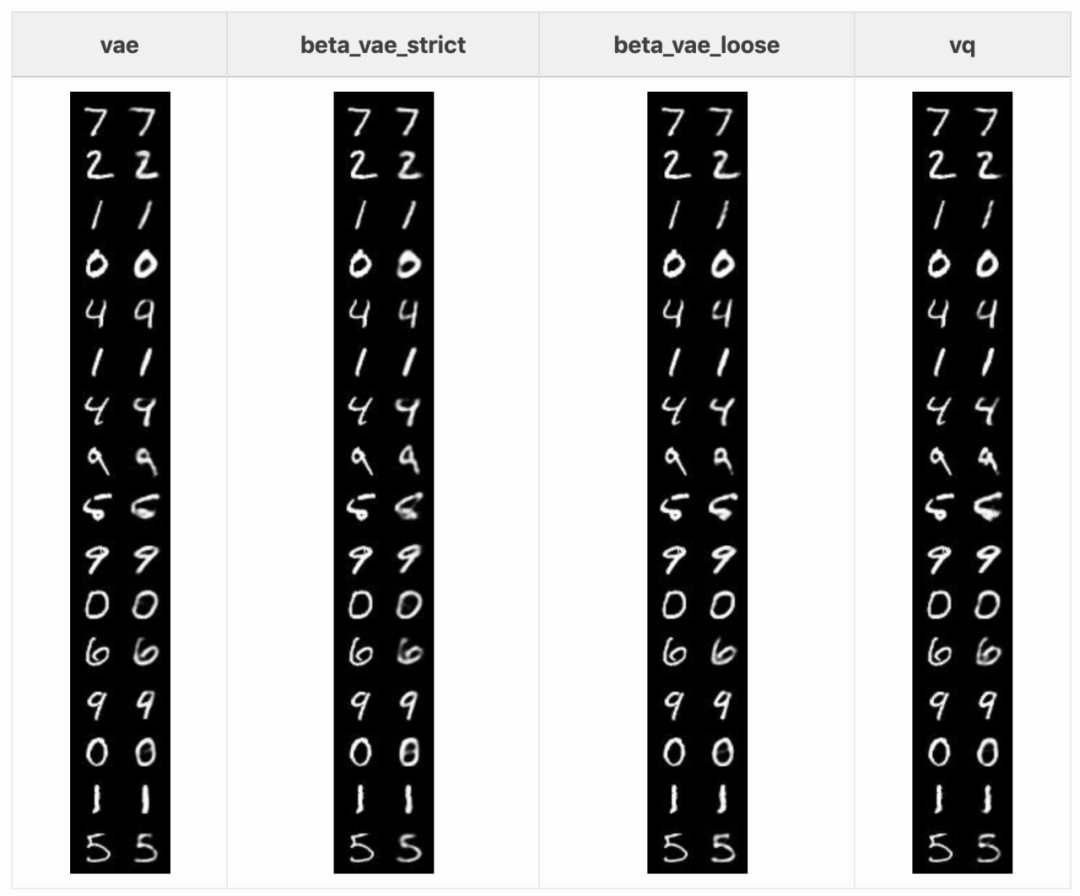

无监督训练用堆叠自编码器是否落伍 Ml博士对比了8个自编码器 深度

数字电子技术digital Electronic Technology 5 组合逻辑电路设计题解题技巧归纳 凝望 划过星空的博客 Csdn博客

數位邏輯學 第八章

Cd4532 8 3线优先编码器以及应用 码农家园

8 3编码器有几个输入端 8线3线编码器有几个输入 8 3线二进制编码器

编码器 常用中规模集成电路 Msi 数电 知乎

74ls148引脚图接法 万图壁纸网

10 9 编码器 解码器 Seq2seq 动手学深度学习 文档

8 3线优先编码器74ls148的级联分析 电子发烧友网

无监督训练用堆叠自编码器是否落伍 Ml博士对比了8个自编码器 深度

電子入門基礎知識之 8 3優先編碼器 每日頭條

數位邏輯學 第八章

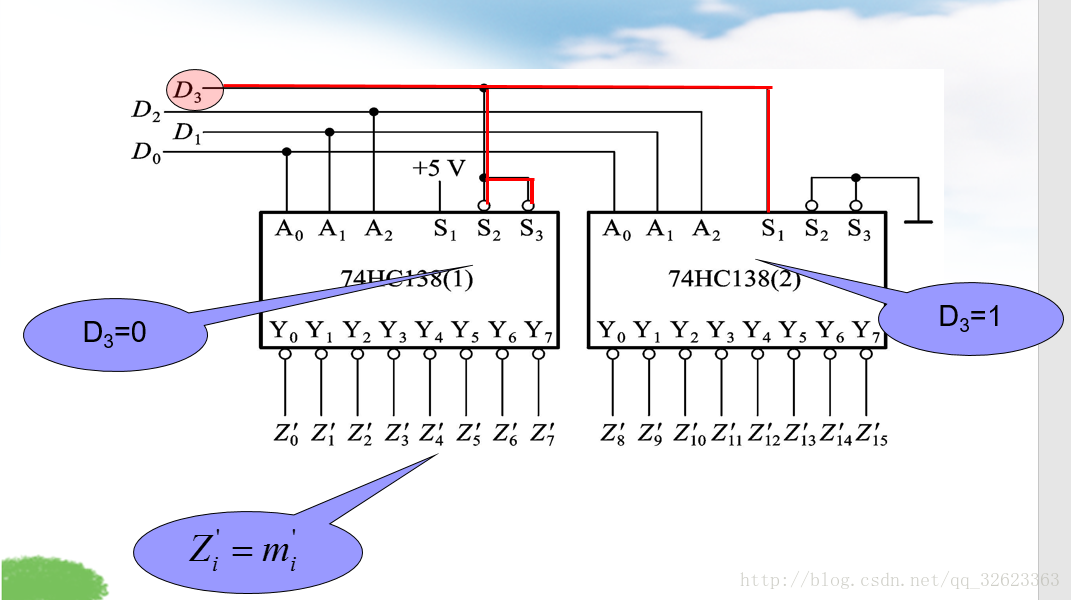

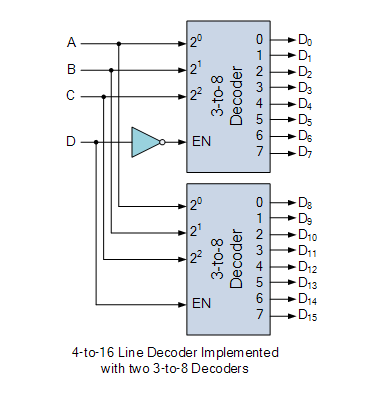

利用74ls148组成16线 4线优先编码器 黑猫警长lee 博客园

编码器 常用中规模集成电路 Msi 数电 知乎

8 3线优先编码器74ls148的级联分析 电子发烧友网

如何用verilog Hdl来实现编码器 Susugreen 的博客 程序员宅基地 Verilog编码器 程序员宅基地

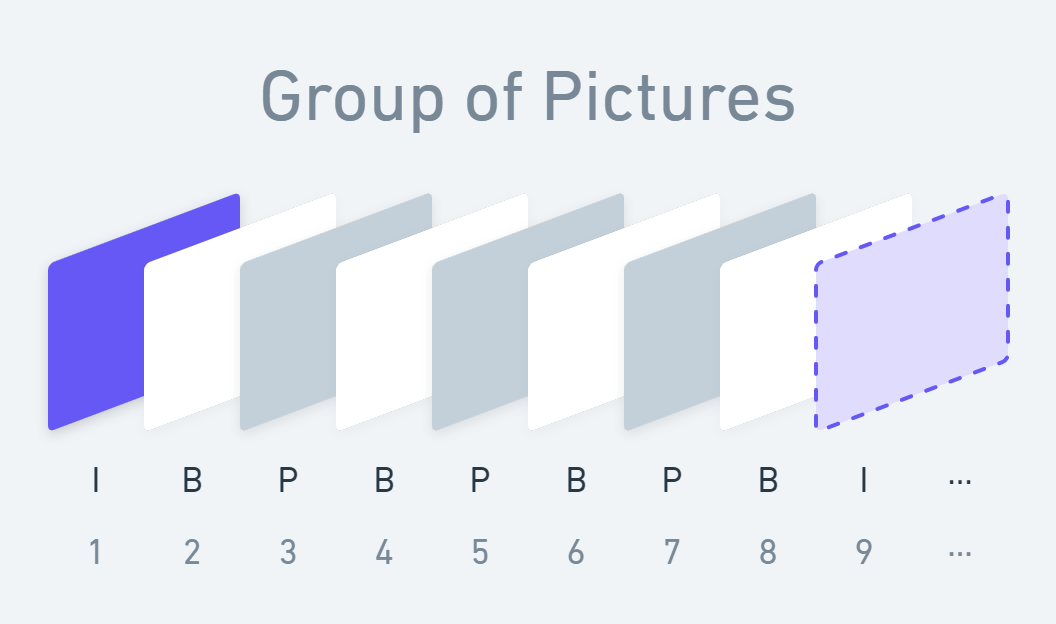

视频帧名词解释 Webrtc 学习指南

编码器 常用中规模集成电路 Msi 数电 知乎

数电第四章总结 组合逻辑电路 吟游诗人 吟唱生命的不朽 Csdn博客

Http Www Ycvs Ntpc Edu Tw Ezfiles 0 1000 Img 112 Pdf

连载 Fpga Verilog Hdl 系列实例 8 3编码器 Weixin 的博客 Csdn博客

8 3编码器 3 8译码器的verilog实现 Sasha Xu 博客园

编码器 常用中规模集成电路 Msi 数电 知乎

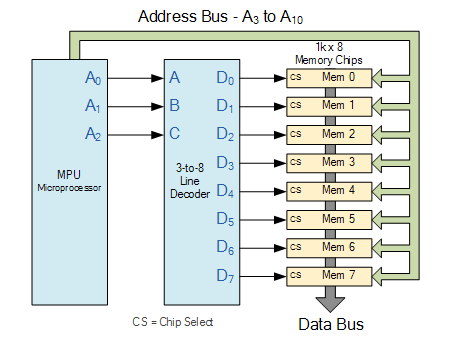

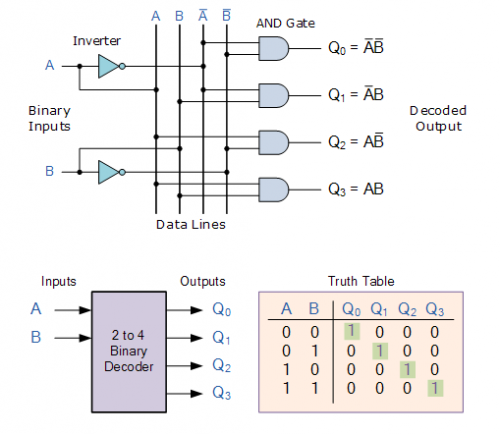

逻辑电路知识 二进制解码器是什么 电子技术基础 面包板社区

编码器 常用中规模集成电路 Msi 数电 知乎

自动编码器一览 一 Kyon Huang 的博客

解碼器 維基百科 自由的百科全書

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

逻辑电路知识 二进制解码器是什么 电子技术基础 面包板社区

无监督训练用堆叠自编码器是否落伍 Ml博士对比了8个自编码器 深度

2

编码器 常用中规模集成电路 Msi 数电 知乎

數位邏輯學 第八章

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

Hello Fpga 编码器 译码器 数据选择器 数值比较器 加法器 每日头条

第四章组合逻辑电路4 1 概述4 2 组合逻辑电路的分析与设计4 3 常用组合逻辑电路4 4 用pld实现组合电路 Ppt Download

J1vv5atfqbi4 M

Cna Rs编码器的编码方法及rs编码器 Google Patents

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

译码器 维基百科 自由的百科全书

組合邏輯的函數functions Of Combination Logic Ppt Video Online Download

编码器和译码器 编码器和译码器实验目的熟悉中规模集成电路编码器 译码器的工作原理和逻辑功能掌握编码器 译码器的级联方法 了解编码器 译码器的应用 Ppt Download

Http Www Ycvs Ntpc Edu Tw Ezfiles 0 1000 Img 112 Pdf

74ls147 万图壁纸网

Www Cyut Edu Tw Yfahuang Chap04 Pdf

深度学习 自动编码器 对称网络结构 华为云

你知道verilog Hdl程序是如何构成的吗 Arm Linux内核驱动学习笔记 Csdn博客

第十六讲编码器 电子常识 电子发烧友网

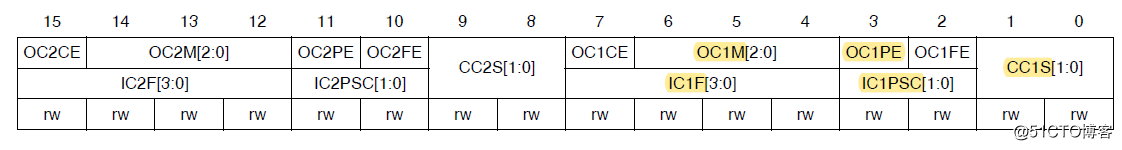

电机控制基础 定时器编码器模式使用与转速计算 码农爱学习 51cto博客

Www Axis Com Files Whitepaper White Paper Video Encoders Zh 2103 Pdf

編碼器原理

常见生成模型 自动编码器auto Encoder 华为云

8 3线优先编码器74ls148的级联分析 电子发烧友网

译码器工作原理 译码器逻辑功能 译码器应用 与非网

數位邏輯學 第八章

數位邏輯學 第八章

2

Lms Hust Edu Tw Sys Read Attach Php Id

Ppt 吳永義powerpoint Presentation Free Download Id

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

Ppt 組合邏輯的函數functions Of Combination Logic Powerpoint Presentation Id

逻辑电路知识 二进制解码器是什么 电子技术基础 面包板社区

Digital System Design Weidong Wang College Of Information

图 74系列数字电路74ls348 8 3线优先编码器 三态 数字电路电路图维库电子市场网

0 件のコメント:

コメントを投稿